Ce que l'on retiendra, c'est que les utilisateurs de plateforme Waimea Bay socket 2011 ne seront pas affectés. Sinon vous pouvez remercier Mr Intel...

Intel devrait dévoiler la première vague de processeurs tirés de l'architecture Sandy Bridge lors du prochain CES, qui se tiendra à Las Vegas en janvier prochain. Nos confrères d'HKEPC ont dévoilé quelques informations supplémentaires à leur sujet. La source de ces informations est très probablement un fabricant de cartes mères taiwanais (voire plusieurs), c'est un point important du fait de leur teneur même.

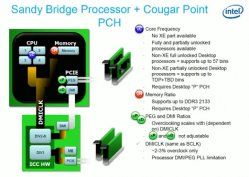

L'architecture Sandy Bridge représente un nouveau pas en matière d'intégration. Le die de ces processeurs Intel sera en effet un véritable concentré de technologie, comptant quatre cœurs, un contrôleur mémoire DDR3, un contrôleur PCI Express, une solution graphique, etc. C'est une petite prouesse, puisque seulement trois ans auparavant, les CPU du géant de Santa Clara ne comptaient même pas d'IMC (Integrated Memory Controller).

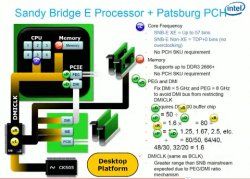

Comme vous le savez sûrement, cette nouvelle architecture sera exploitée par deux types de processeurs distincts (deux plateformes en réalité). Les Sandy Bridge lancés au CES 2011 seront des processeurs à quatre cœurs, d'entrée et de milieu-de-gamme. Ils adopteront le socket LGA 1155, ne dépasseront pas les 95 watts de TDP et fonctionneront avec les chipsets Cougar Point. Quelques mois plus tard, Intel présentera les Sandy Bridge E, des solutions haut-de-gamme qui disposeront de six à huit cœurs et qui prendront place sur un socket LGA 2011. Ils formeront, avec le chipset Patsburg, la plateforme Waimea Bay.

La grande nouvelle, c'est que les processeurs Sandy Bridge ne pourront visiblement pas s'overclocker par le bus ! Pour comprendre le pourquoi du comment, il faut revenir sur la façon dont les solutions actuelles et passées génèrent les différentes fréquences au cœur d'un ordinateur.

C'est le BIOS de la carte mère qui se charge de fixer ces fréquences, qui sont générées par une petite puce qu'on appelle généralement PLL. Ces solutions suivent des spécifications définies par Intel (CK410, CK505) et disposent également de fonctions « propres » plus ou moins avancées (les deux choses étant également liées). Les PLL les plus anciennes nécessitaient un réglage manuel (les fameux cavaliers) tandis que les plus récentes sont contrôlables à la volée depuis Windows.

Il y a quelques années, suivant la conception de la carte mère de son chipset, la gestion de la fréquence du FSB était « fixée » ou non, c'est-à-dire qu'elle était gérée indépendamment des fréquences des bus PCI et AGP, ou pas. C'était un point critique pour l'overclockeur, puisque si faire varier le FSB (et en conséquence la fréquence finale du processeur) ne pose pas de problème tant qu'on ne dépasse pas une certaine limite, toucher au bus PCI et AGP fut toujours problématique. Quelques MHz de plus suffisaient à générer des corruptions...

Avec l'architecture Sandy Bridge, Intel a choisi d'intégrer la gestion des fréquences dans le PCH (Platform Controller Hub, le P67 Express pour notre exemple). C'est-à-dire que les fréquences des cœurs du processeur, mais également celles du PCIE, du SATA, de l'USB, de l'UNCORE, de la DDR3, etc., sont désormais gérées ensemble. Du point de vue d'Intel, c'est logique, cela réduit le nombre de puces présentes sur le circuit imprimé et cela garantit une meilleure fiabilité en plus d'en réduire le coût. Pour l'overclockeur, c'est sans appel, le DMICLK (qui remplace donc le BCLK) ne pouvant être augmenté que de quelques pourcents... S'en est finit de l'overclocking !

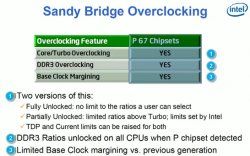

Si pour Intel, les overclockeurs ne représentent qu'une fraction de sa clientèle, ce n'est évidemment pas le cas de certains fabricants de cartes mères taiwanais (c'est sans doute pour cette raison qu'ils ont laissé filtrer ces informations). Le géant de Santa Clara va donc contourner le problème qu'il a créé en libérant partiellement le coefficient multiplicateur. En réalité, c'est une refonte considérable du mode Turbo Boost. En premier lieu, le TDP ne sera plus une limite. Ce changement est très important puisqu'il met tout simplement à mort le concept de « fréquence de base » sur ces processeurs (un concept déjà bien malmené depuis l'arrivée du Turbo Boost).

Intel proposera des Sandy Bridge « complètement débridés » sur lesquels la seule limite sera le nombre de bins (57, si un bin correspond toujours à 133 MHz, cela équivaudra à pas moins de 7,6 GHz). Il y a fort à parier qu'il s'agisse là des fameux processeurs K. Il existera également des CPU « partiellement débridés » limités à un certain nombre de bins en plus. Dans tous les cas, une carte mère équipée d'un chipset P sera nécessaire. À noter également, ces solutions supporteront la DDR3 jusqu'à 2133 MHz (à l'aide de ratio).

Du côté de la plateforme Waimea Bay (les Sandy Bridge en LGA 2011, montés sur une carte mère équipée du chipset Patsburg), les choses sont plus simples, on retrouve une PLL « à l'ancienne » et donc un overclocking plus classique. Cependant, Intel maintient une limite de 57 bins (probablement pour les coefficients Turbo Boost) sur les XE et indique que certains processeurs seront entièrement bloqués à ce niveau. La fréquence maximale supportée pour la DDR3 passera quant à elle à 2666 MHz.

Évidemment, on se souviendra qu'avant le lancement des premiers Core i7, certains avaient également affirmé que l'architecture Nehalem signerait la fin de l'overclocking. De plus, les détails restent peu nombreux même si ces derniers semblent cohérents. Il faudra encore attendre quelques mois avant de pouvoir vérifier tout cela avec des tests concrets. Rendez-vous en 2011..

Source : PC World